# EE 330 Lecture 35

**Cascaded Amplifiers**

**Differential Amplifiers**

**Amplifier Biasing**

Other Amplifier Structures

High Frequency Performance of Amplifiers

Parasitic Capacitances in MOS Devices

### Fall 2025 Exam Schedule

Exam 1 Friday Sept 26

Exam 2 Friday October 24

Exam 3 Friday Nov 21

Final Exam Monday Dec 15 12:00 - 2:00 PM

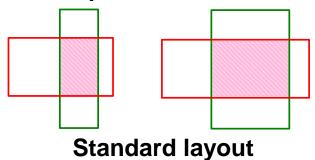

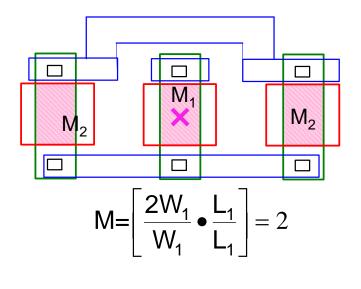

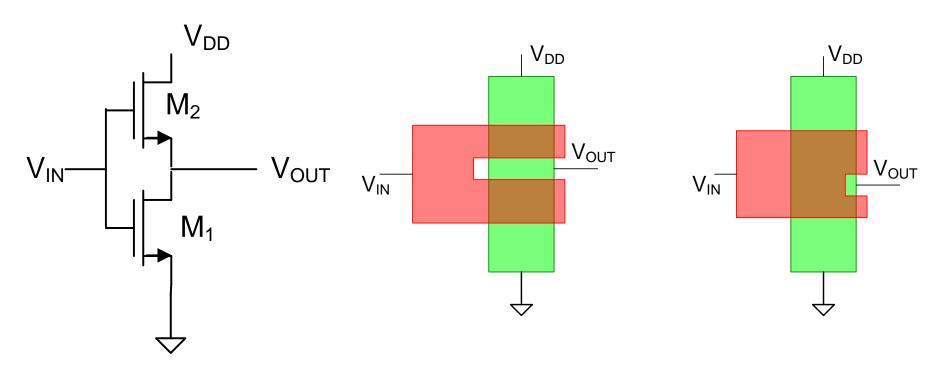

# Layout of Current Mirrors

#### Example with M = 2

$$M = \left[ \frac{W_2}{W_1} \frac{L_1}{L_2} \right]$$

$$\mathsf{M} = \left[ \frac{2\mathsf{W}_1 + 4\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right] = 2$$

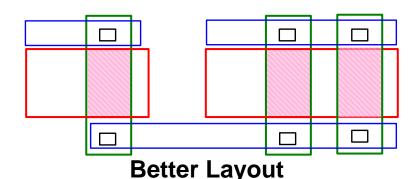

**Even Better Layout**

$$\mathsf{M} = \left\lceil \frac{2\mathsf{W}_1 + 4\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right\rceil = 2$$

- This is termed a common-centroid layout

- Linear gradient mismatch eliminated with common-centroid layout!

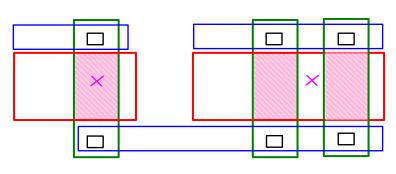

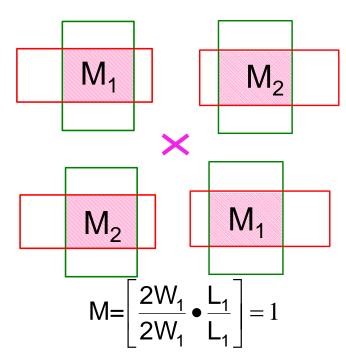

### Layout of Matching-Critical Circuits

#### Example with M = 2

**Common-centroid Layout**

Theorem: Linear gradient mismatch eliminated with

common- centroid layout!

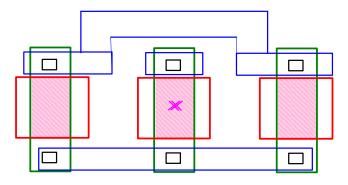

# Common-Centroid Layouts

- Individual transistors often decomposed into parallel multiple unary devices connected in parallel

- Common-Centroid layout approach widely used to minimize (ideally cancel) gradient effects in matching-critical circuits

- Applications extend well beyond current mirrors

- More than 2 devices can share a common centroid

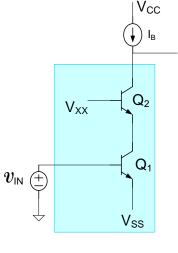

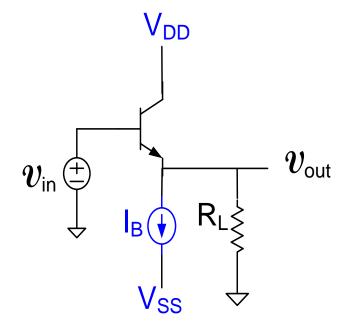

$V_{SS}$

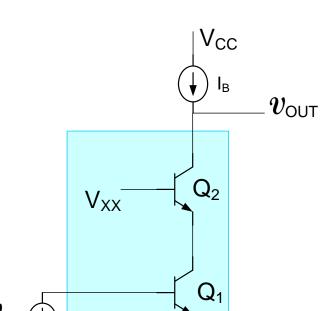

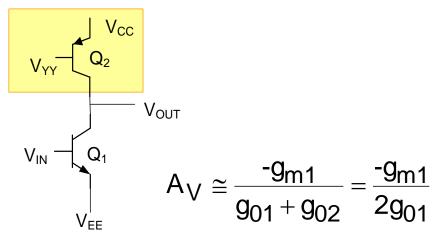

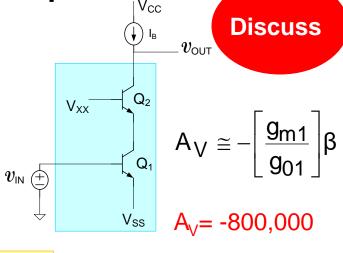

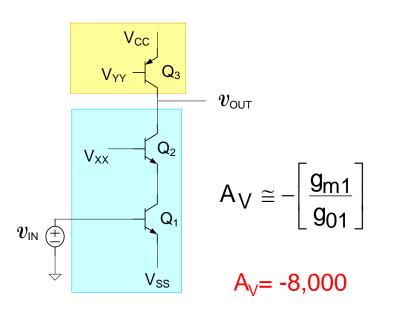

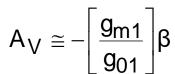

$$A_{VCC} \cong - \left[ \frac{g_{m1}}{g_{02}} \beta \right] \cong - \left[ \frac{g_{m1}}{g_{01}} \right] \beta$$

$$g_{OCC} \cong \frac{g_{O2}}{\beta}$$

$$A_{VCC} \cong -\left[\frac{g_{m1}}{g_{01}}\right]\beta = \left[\frac{2V_{AF}}{V_t}\right]\beta = \left[-8000\right]100$$

$$A_{VCC} \cong -800,000$$

This gain is very large and only requires two transistors!

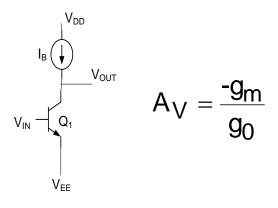

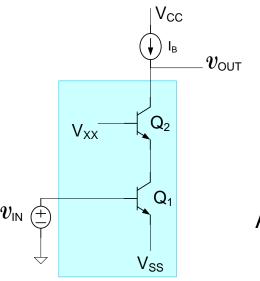

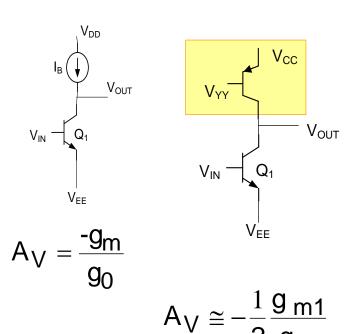

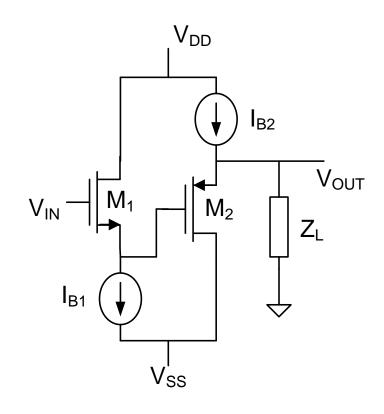

What happens to the gain if a transistor-level current source is used for I<sub>B</sub>?

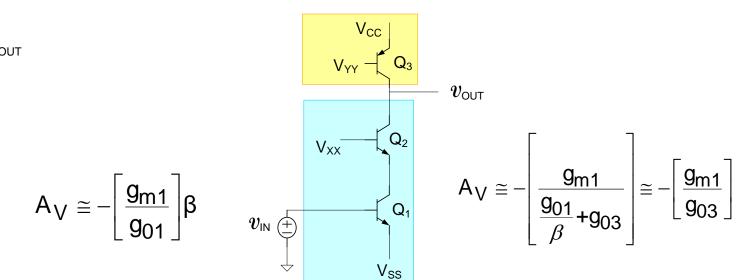

$$A_{V} \cong A_{VCC} \left[ \frac{g_{0CC}}{g_{03}} \right] \cong \frac{A_{VCC}}{\beta}$$

**But recall**

$$A_{VCC} \cong - \left| \frac{g_{m1}}{g_{01}} \right| \beta$$

**Thus**

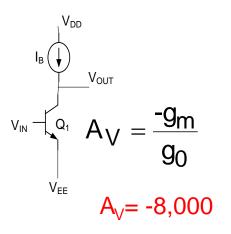

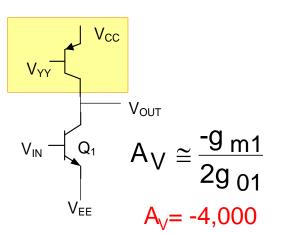

$$A_{V} \cong - \left[ \frac{g_{m1}}{g_{01}} \right]$$

$$A_{V} \cong - \begin{bmatrix} I_{CQ} \\ V_{t} \\ I_{CQ} \\ V_{AF} \end{bmatrix} = - \begin{bmatrix} V_{AF} \\ V_{t} \end{bmatrix} \cong -8000$$

- This is still a factor of 2 better than that of the CE amplifier with transistor current source  $A_{VCE} \cong -\left[\frac{g_{m1}}{2g_{01}}\right]$

- It only requires one additional transistor

- But its not nearly as good as the gain the cascode circuit seemed to provide 9 of 75

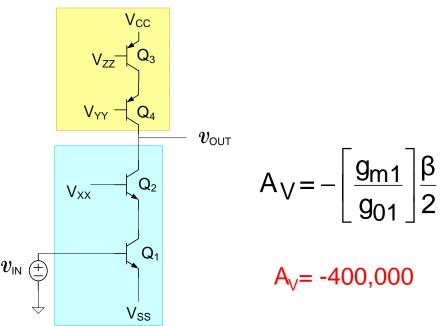

### Cascode Configuration Comparisons

$$A_{V} \cong - \left| \frac{g_{m1}}{g_{01}} \right| \beta$$

Gain limited by output impedance of current scource !!

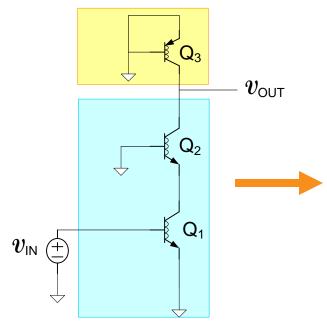

Can we design a better current source? In particular, one with a higher output impedance?

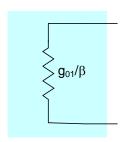

### Better current sources

Need a higher output impedance than go

The output impedance of the cascode circuit itself was very large!

$$g_{OCC} \cong \frac{g_{O1}}{\beta}$$

Can a current source be built with the cascode circuit?

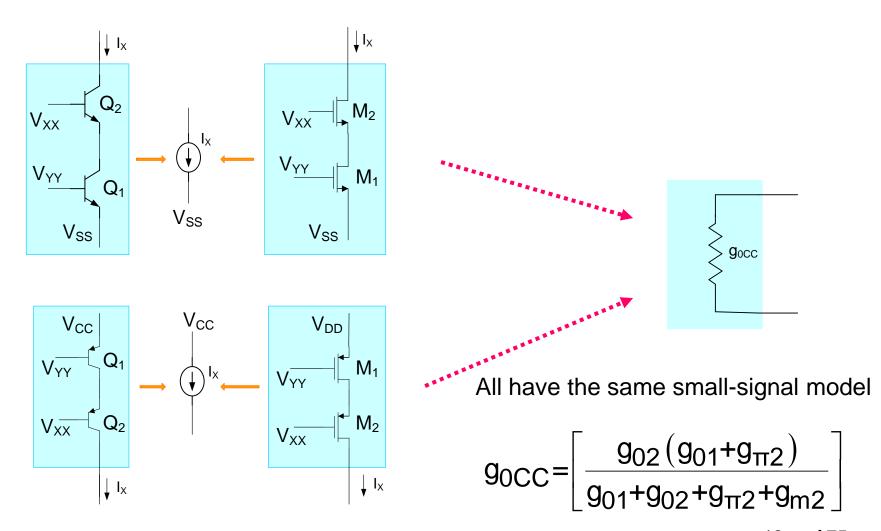

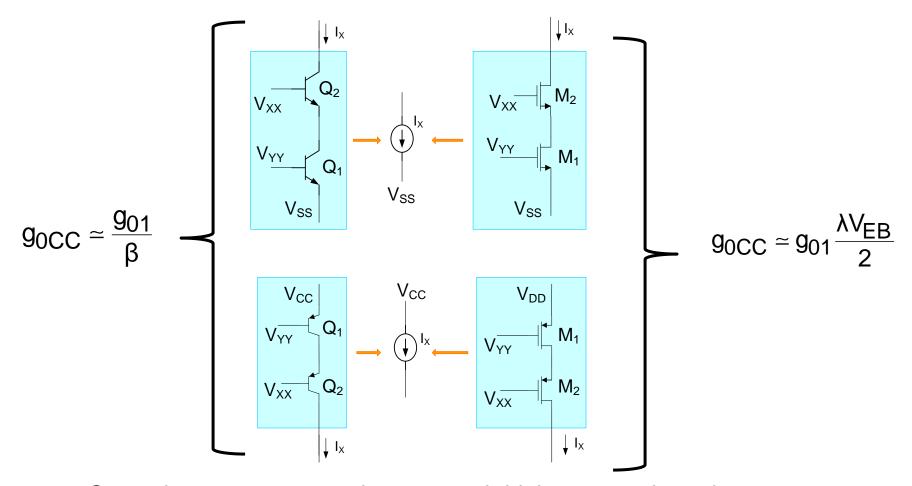

### Cascode current sources

12 of 75

### Cascode current sources

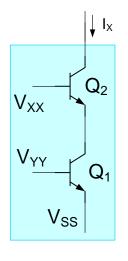

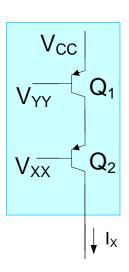

#### For the BJT cascode current sources

$$g_{0CC} = \left[ \frac{g_{02} (g_{01} + g_{\pi 2})}{g_{01} + g_{02} + g_{\pi 2} + g_{m2}} \right] \approx \left[ \frac{g_{02} g_{\pi 2}}{g_{m2}} \right] = \frac{g_{01}}{\beta}$$

### Cascode current sources

- Cascode current sources have a much higher output impedance that the basic single-transistor current sources

- No increase in power dissipation (current re-use concept)

- Moderate loss in headroom

Cascode Configuration Comparisons

### High Gain Amplifier Comparisons (BJT)

$v_{\scriptscriptstyle \mathsf{OUT}}$

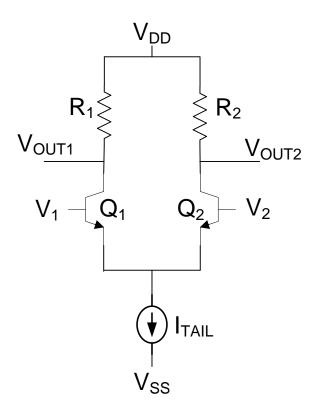

- Single-ended high-gain amplifiers inherently difficult to bias (because of the high gain) Biasing becomes practical when used in

- differential applications

- These structures are widely used but usually with differential inputs

of 75

#### **Review From Previous Lecture**

### High Gain Amplifier Comparisons (n-ch MOS)

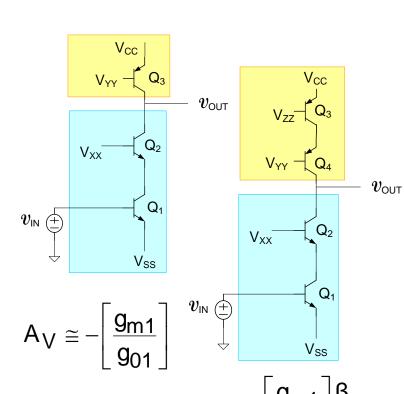

#### Two-stage CE:CE or CS:CS Cascade

$$A_{VCB} = ?$$

$$A_{VCM} = ?$$

#### Two-stage CE:CE or CS:CS Cascade

$$A_{VCB} \cong \left[\frac{-g_{m1}}{g_{01}+g_{\pi 2}}\right] \left[\frac{-g_{m2}}{g_{02}}\right] \cong \frac{g_{m1}g_{m2}}{g_{\pi 2}g_{02}} = \beta \frac{g_{m1}}{g_{02}}$$

$$A_{VCM} = \left[\frac{-g_{m1}}{g_{01}}\right] \left[\frac{-g_{m2}}{g_{02}}\right] = \frac{g_{m1}g_{m2}}{g_{01}g_{02}}$$

- Significant increase in gain

- Gain is noninverting

- Comparable to that obtained with the cascode but noninverting

#### Two-stage CE:CE or CS:CS Cascade

$$A_{VCB} \cong \left[ \frac{-g_{m1}}{g_{01} + g_{03} + g_{\pi 2}} \right] \left[ \frac{-g_{m2}}{g_{02} + g_{04}} \right] \cong \frac{g_{m1}g_{m2}}{2g_{\pi 2}g_{02}} = \beta \frac{g_{m1}}{2g_{02}}$$

$$A_{VCM} = \left[ \frac{-g_{m1}}{g_{01} + g_{03}} \right] \left[ \frac{-g_{m2}}{g_{02} + g_{04}} \right] = \frac{g_{m1}g_{m2}}{4g_{01}g_{02}}$$

Note factor or 2 and 4 reduction in gain due to actual current source bias

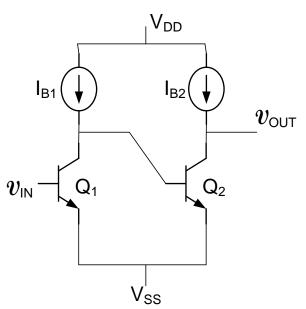

**Two-stage CE Cascade**

**Three-stage CE Cascade**

- Large gains can be obtained by cascading

- Gains are multiplicative (when loading is included)

- Large gains used to build "Op Amps" and feedback used to control gain value

- Some attention is needed for biasing but it is manageable

- Minor variant of the two-stage cascade often used to build Op Amps

- Compensation of two-stage cascade needed if feedback is applied to maintain stability

- For many years three or more stages were seldom cascaded because of challenges in compensation to maintain stability though recently some industrial adoptions

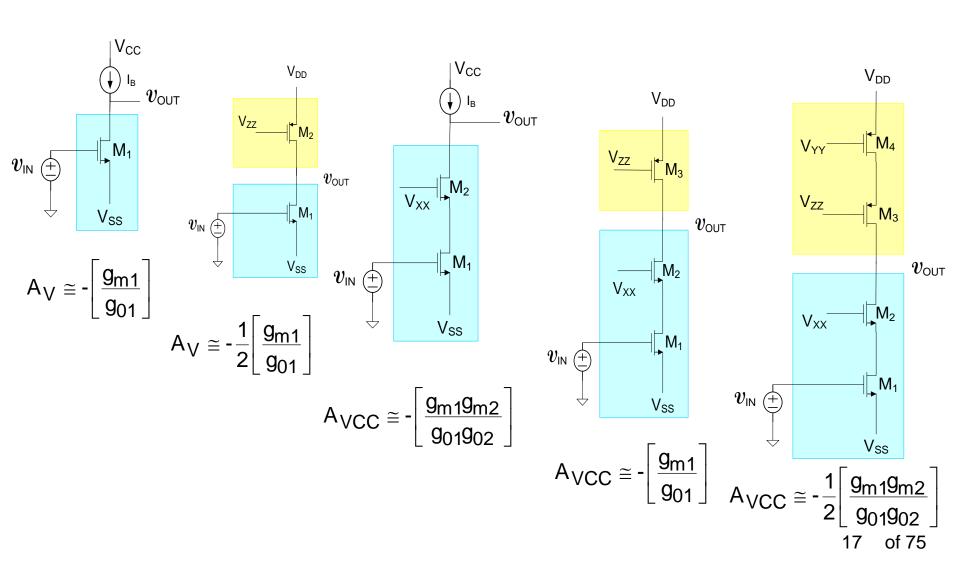

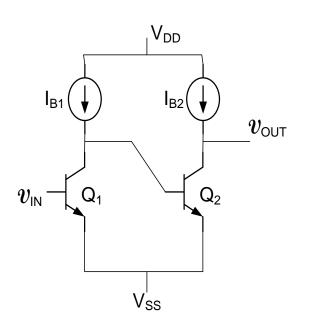

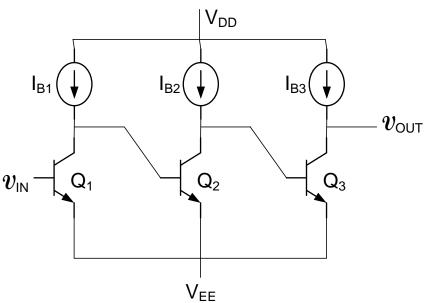

## Differential Amplifiers

A basic operational amplifier circuit

# Differential Amplifiers

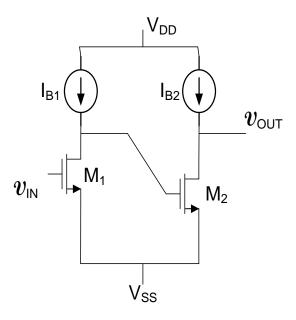

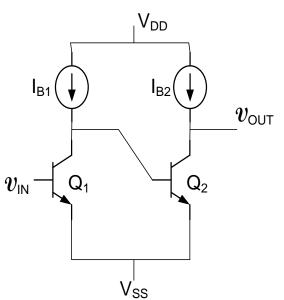

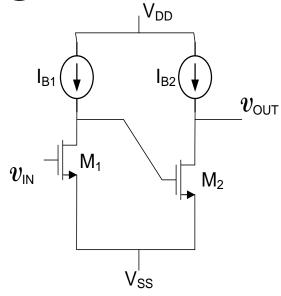

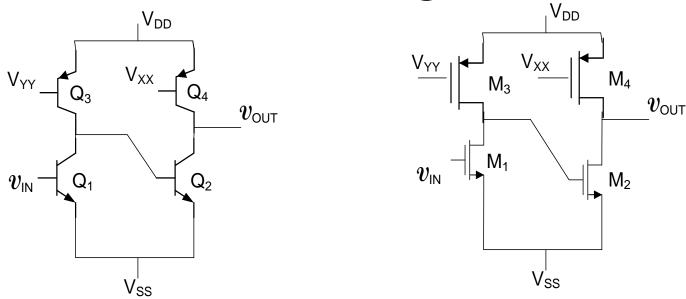

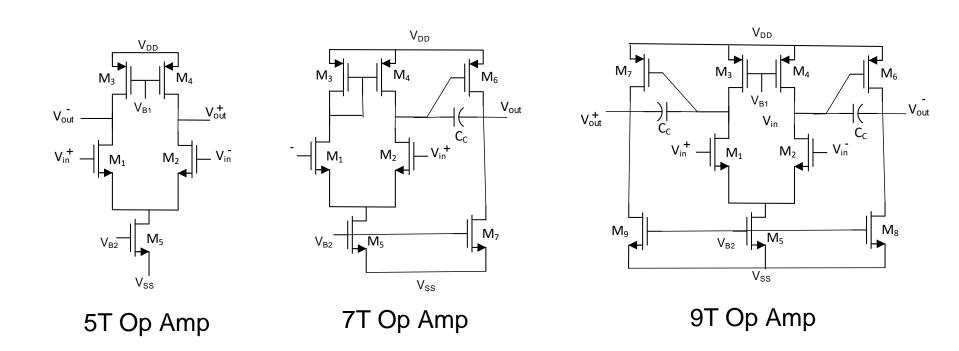

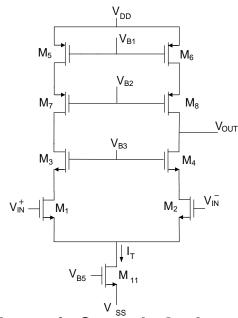

#### Basic MOS operational amplifier circuits

(CMFB not shown for 9T op amp)

### The Cascode Amplifier

- Operational amplifiers often built with basic cascode configuration

- CMFB used to address the biasing problem

- Usually configured as a differential structure when building op amps

- Have high output impedance (but can be bufferred)

- Terms "telescopic cascode", "folded-cascode", and "regulated cascode" often refer to op amps based upon the cascode configuration

29 of 75

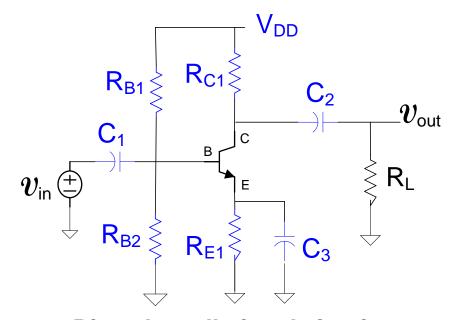

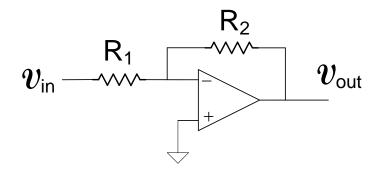

Amplifier biasing is that part of the design of a circuit that establishes the desired operating point (or Q-point)

Goal is to invariably minimize the impact the biasing circuit has on the small-signal performance of a circuit

Usually at most 2 dc power supplies are available and these are often fixed in value by system requirements – this restriction is cost driven

Discrete amplifiers invariable involve adding biasing resistors and use capacitor coupling and bypassing

Integrated amplifiers often use current sources which can be used in very large numbers and are very inexpensive

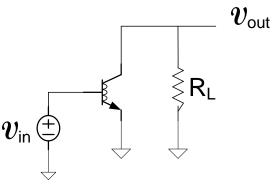

$$A_V = -g_m R_L$$

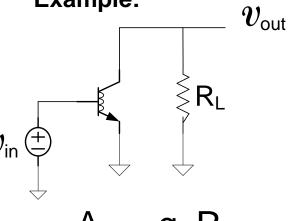

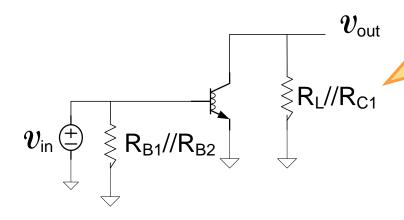

**Desired small-signal circuit Common Emitter Amplifier**

**Actual small-signal circuit**

$$A_V = -g_m (R_L // R_{C1})$$

#### **Example:**

Desired small-signal circuit Common Emitter Amplifier

**Biased small-signal circuit**

#### **Example:**

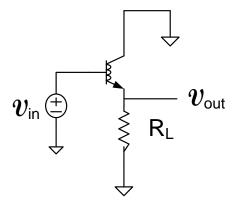

# Desired small-signal circuit Common Collector Amplifier

#### **Example:**

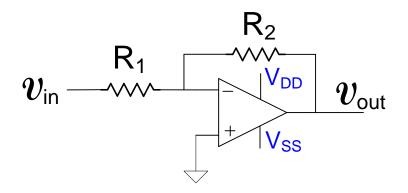

**Desired small-signal circuit Inverting Feedback Amplifier**

**Biased circuit**

#### **Basic Amplifier Structures**

- 1. Common Emitter/Common Source

- 2. Common Collector/Common Drain

- 3. Common Base/Common Gate

- 4. Common Emitter with R<sub>E</sub>/ Common Source with R<sub>S</sub>

- 5. Cascode (actually CE:CB or CS:CG cascade)

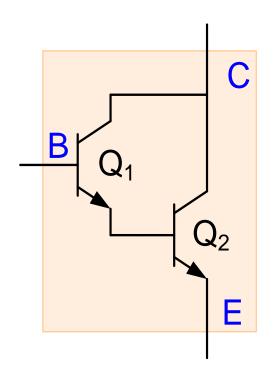

- 6. Darlington (special CC:CC or CD:CD (approx) cascade) Will be discussed later

The first 4 are most popular

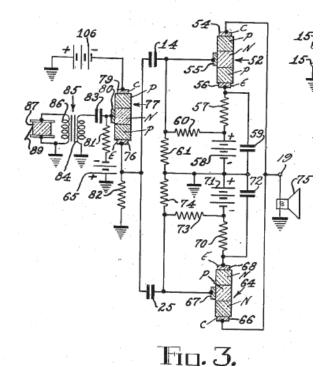

**Darlington Configuration**

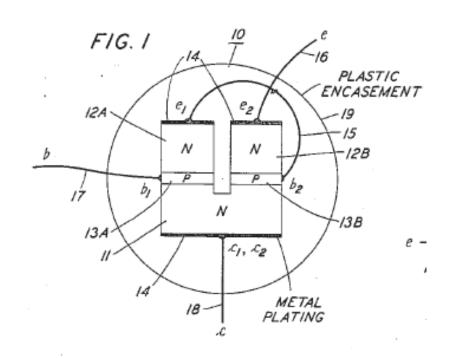

S. DARLINGTON

2,663,806

SEMICONDUCTOR SIGNAL TRANSLATING DEVICE

Filed May 9, 1952

- Current gain is approximately β<sup>2</sup>

- Two diode drop between B<sub>eff</sub> and E<sub>eff</sub>

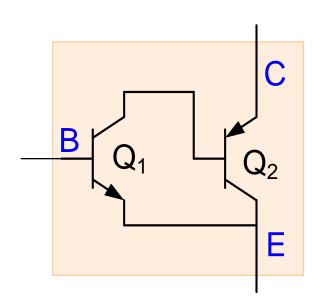

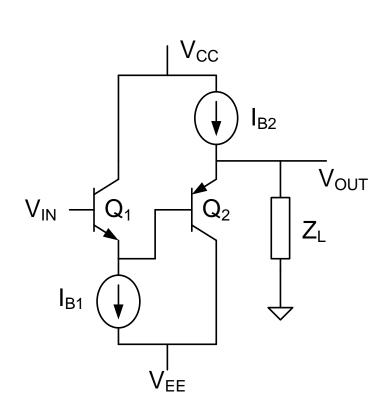

Sziklai Pair

May 7, 1957

G. C. SZIKLAI

2,791,644

PUSH-PULL AMPLIFIER WITH COMPLEMENTARY TYPE TRANSISTORS

Filed Nov. 7, 1952

- Gain similar to that of Darlington Pair

- Current gain is approximately β<sub>n</sub> β<sub>p</sub>

- Current gain will not be as large when  $\beta_p < \beta_n$

- Only one diode drop between B<sub>eff</sub> and E<sub>eff</sub>

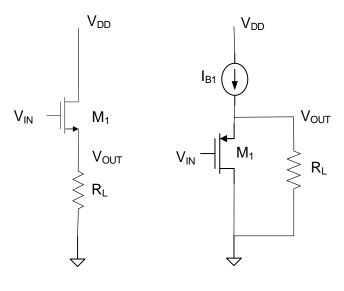

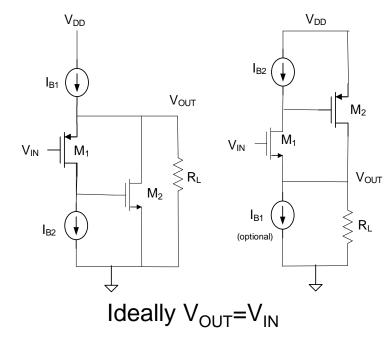

#### **Buffer**

### Super Buffer

Ideally V<sub>OUT</sub>=V<sub>IN</sub>

Assume load terminated on gnd

Current through shift transistor is constant for Super Buffer as  $V_{\rm IN}$  changes so voltage shift does not change with  $V_{\rm IN}$

Same nominal voltage shift as buffer

#### Low offset buffers

- Actually a CC-CC or a CD-CD cascade

- Significant drop in offset between input and output

- Biasing with DC current sources

- Can Add Super Buffer to Output

#### **Voltage Attenuator**

- Attenuation factor is quite accurate (Determined by geometry)

- Infinite input impedance

- M<sub>1</sub> in triode, M<sub>2</sub> in saturation

- Actually can be a channel-tapped structure

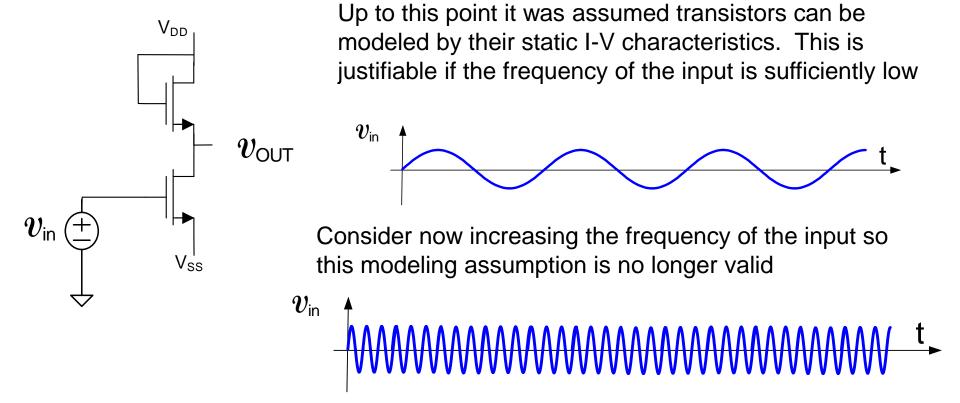

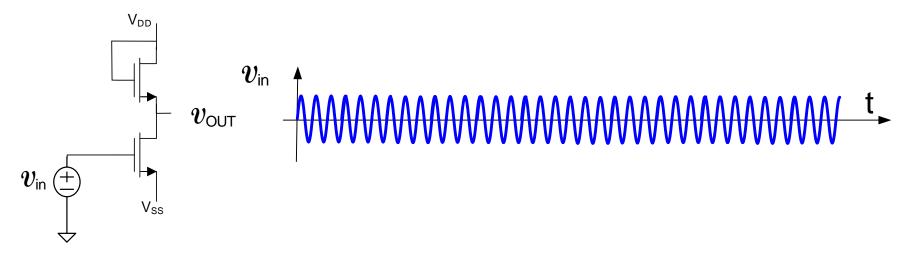

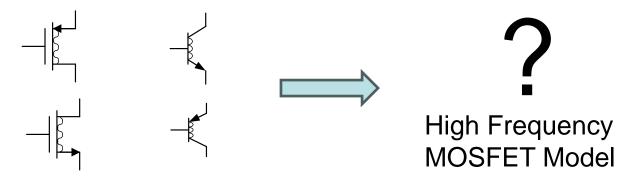

### High Frequency Amplifier Performance

As was observed earlier in the course with digital circuits, parasitic capacitors in the MOS transistors will limit the high frequency performance

### High Frequency Amplifier Performance

Parasitic capacitors in the MOS transistors will limit the high frequency performance

How can we predict performance of amplifiers (with small-signal inputs) at high frequencies?

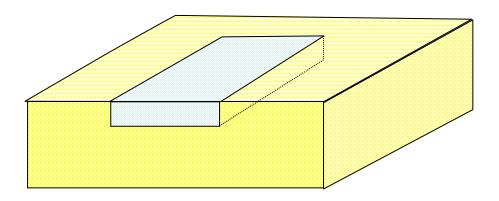

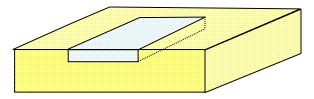

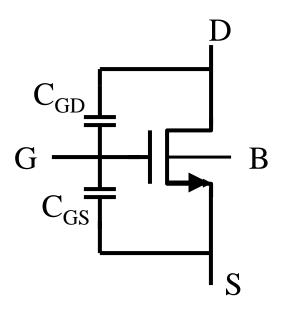

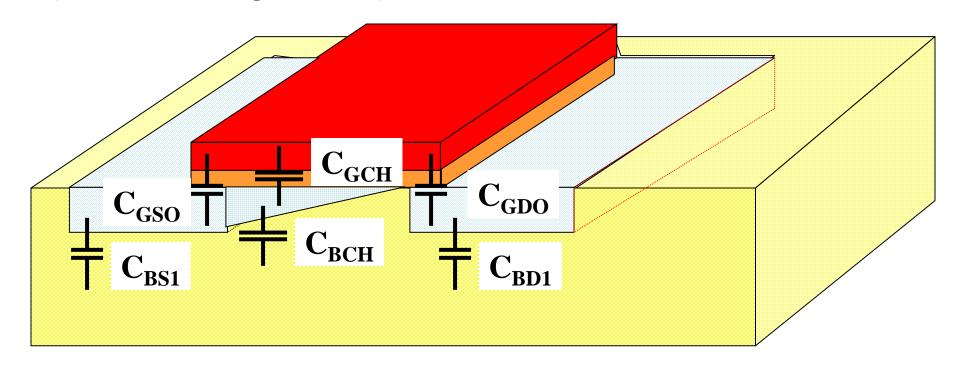

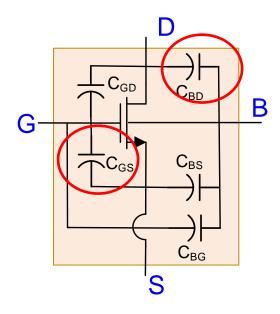

# Parasitic Capacitors in MOSFET

- This capacitance was modeled previously and exists when the transistor is operating in triode or saturation

- But there are others that also affect high-frequency or high-speed operation

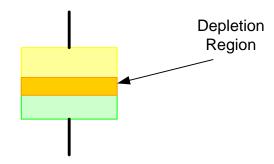

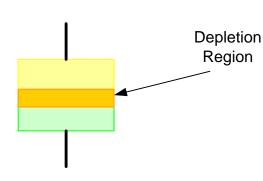

Recall that pn junctions have a depletion region!

pn junction capacitance

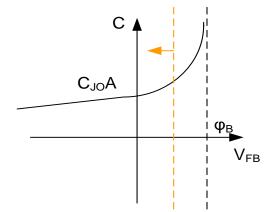

For  $V_{FB} < \varphi_B/2$

$$C = \frac{C_{J0}A}{\left(1 - \frac{V_{FB}}{\phi_{B}}\right)^{n}}$$

pn junction capacitance

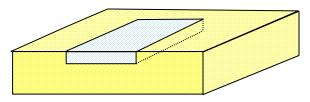

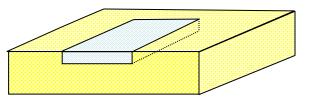

The bottom and the sidewall:

pn junction capacitance

For a pn junction capacitor

$$C_{\text{BOT}}A+C_{\text{SW}}P$$

$$C_{BOT} = \frac{C_{BOTO}}{\left(1 - \frac{V_{FB}}{\phi_{B}}\right)^{m}}$$

$$C_{sw} = \frac{C_{swo}}{\left(1 - \frac{V_{FB}}{\Phi_{B}}\right)^{m}}$$

A: Junction Area

P: Junction Perimeter

V<sub>FB</sub>: forward bias on junction

Model Parameters:

$\{C_{BOT0}, C_{SW0}, \phi_B, m\}$

C<sub>BOT</sub> and C<sub>SW</sub> are capacitance densities

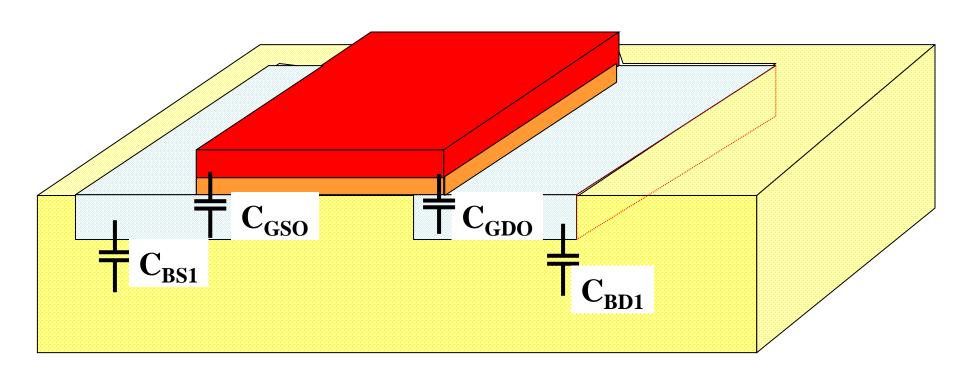

### Types of Capacitors in MOSFETs

1. Fixed Capacitors

- a. Fixed Geometry

- b. Junction

- 2. Operating Region Dependent

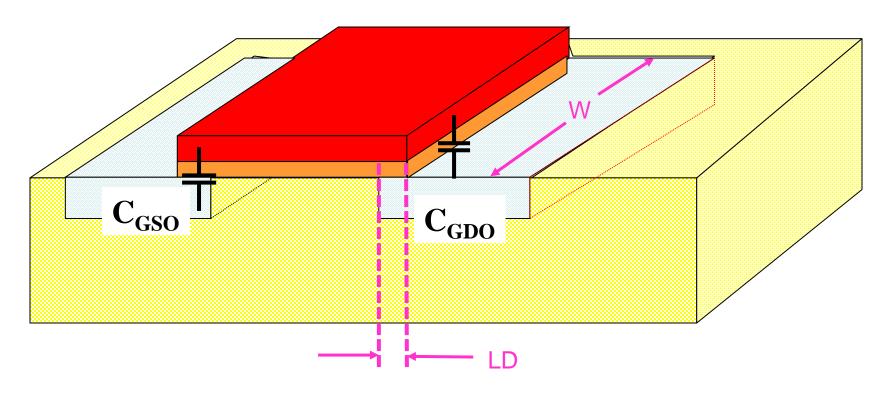

#### **Fixed Capacitors – Fixed Geometry**

Overlap Capacitors: C<sub>GDO</sub>, C<sub>GSO</sub>

L<sub>D</sub>: lateral diffusion

Cap Density: Cox

## Parasitic Capacitance Summary (partial)

|                  | Cutoff             | Ohmic              | Saturation |

|------------------|--------------------|--------------------|------------|

| C <sub>GSO</sub> | CoxWL <sub>D</sub> | CoxWL <sub>D</sub> | $CoxWL_D$  |

| C <sub>GDO</sub> | CoxWL <sub>D</sub> | CoxWL <sub>D</sub> | $CoxWL_D$  |

#### Overlap Capacitance Model Parameters

| CAPACITANCE PARAMETERS |     | P+ I |       | M1 | M2 | МЗ | M4 | M5 | M6 | R_W | D_N_W M51 |     | UNITS   |

|------------------------|-----|------|-------|----|----|----|----|----|----|-----|-----------|-----|---------|

| Area (substrate)       | 942 | 1163 | 3 106 | 34 | 14 | 9  | 6  | 5  | 3  |     | 123       | 125 | aF/um^2 |

| Area (N+active)        |     |      | 8484  | 55 | 20 | 13 | 11 | 9  | 8  |     |           |     | aF/um^2 |

| Area (P+active)        |     |      | 8232  |    |    |    |    |    |    |     |           |     | aF/um^2 |

| Area (poly)            |     |      |       | 66 | 17 | 10 | 7  | 5  | 4  |     |           |     | aF/um^2 |

| Area (metal1)          |     |      |       |    | 37 | 14 | 9  | 6  | 5  |     |           |     | aF/um^2 |

| Area (metal2)          |     |      |       |    |    | 35 | 14 | 9  | 6  |     |           |     | aF/um^2 |

| Area (metal3)          |     |      |       |    |    |    | 37 | 14 | 9  |     |           |     | aF/um^2 |

| Area (metal4)          |     |      |       |    |    |    |    | 36 | 14 |     |           |     | aF/um^2 |

| Area (metal5)          |     |      |       |    |    |    |    |    | 34 |     | (         | 84  | aF/um^2 |

| Area (r well)          | 920 | )    |       |    |    |    |    |    |    |     |           |     | aF/um^2 |

| Area (d well)          |     |      |       |    |    |    |    |    |    | 582 |           |     | aF/um^2 |

| Area (no well)         | 137 | 7    |       |    |    |    |    |    |    |     |           |     | aF/um^2 |

| Fringe (substrate)     | 212 | 2 23 | 35    | 41 | 35 | 29 | 21 | 14 |    |     |           |     | aF/um   |

| Fringe (poly)          |     |      |       | 70 | 39 | 29 | 23 | 20 | 17 |     |           |     | aF/um   |

| Fringe (metal1)        |     |      |       |    | 52 | 34 |    | 22 | 19 |     |           |     | aF/um   |

| Fringe (metal2)        |     |      |       |    |    | 48 | 35 | 27 | 22 |     |           |     | aF/um   |

| Fringe (metal3)        |     |      |       |    |    |    | 53 | 34 | 27 |     |           |     | aF/um   |

| Fringe (metal4)        |     |      |       |    |    |    |    | 58 | 35 |     |           |     | aF/um   |

| Fringe (metal5)        |     |      |       |    |    |    |    |    | 55 |     |           |     | aF/um   |

| Overlap (N+active)     |     |      | 89    | 5  |    |    |    |    |    |     |           |     | aF/um   |

| Overlap (P+active)     |     |      | 73    | 7  |    |    |    |    |    |     |           |     | aF/um   |

|                        |     |      |       |    |    |    |    |    |    |     |           |     |         |

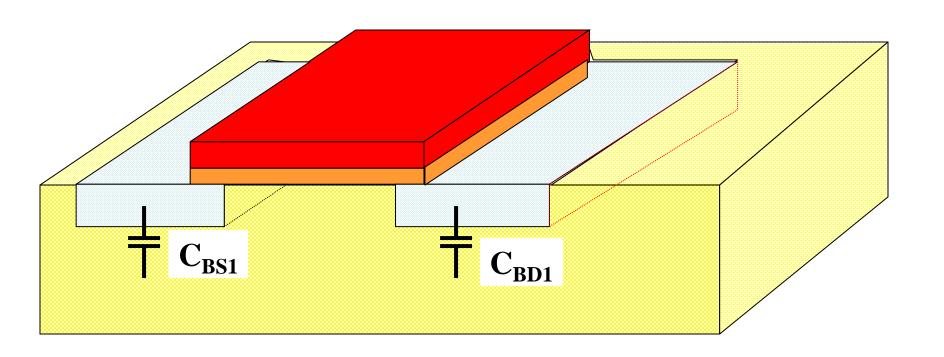

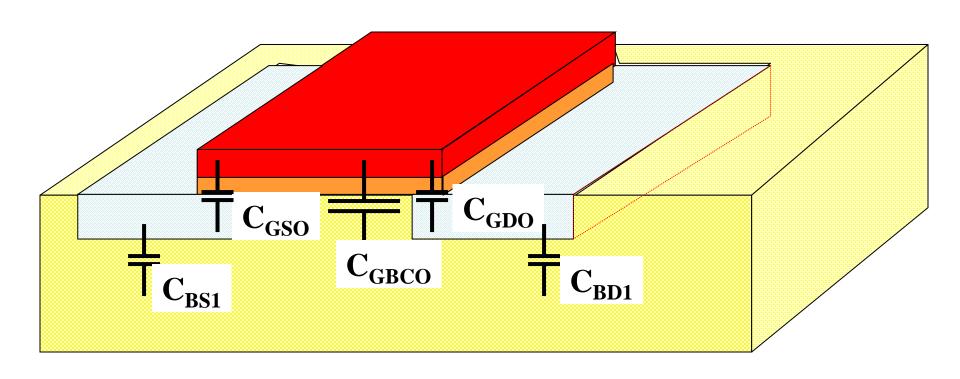

## Types of Capacitors in MOSFETs

- 1. Fixed Capacitors

- a. Fixed Geometry

- b. Junction

- 2. Operating Region Dependent

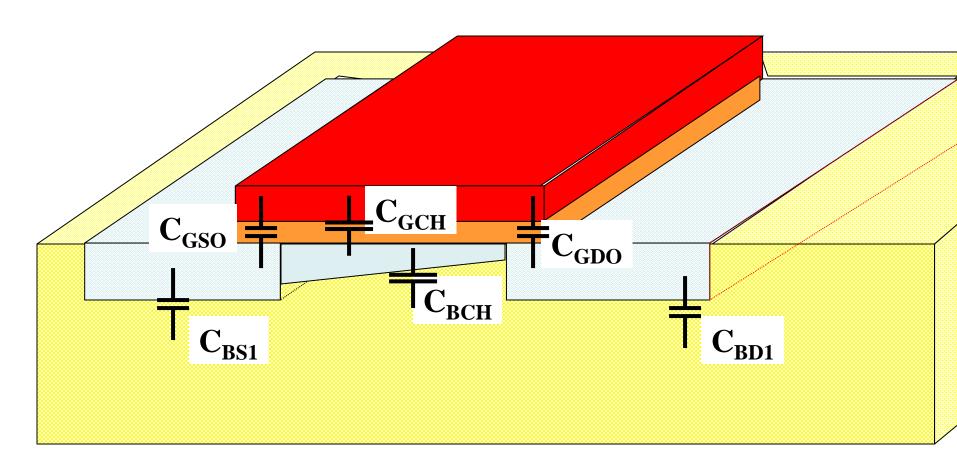

### Parasitic Capacitors in MOSFET Fixed Capacitors- Junction

Junction Capacitors: C<sub>BS1</sub>, C<sub>BD1</sub>

- Fixed Capacitors

Overlap Capacitors: C<sub>GDO</sub>, C<sub>GSO</sub>

Junction Capacitors: C<sub>BS1</sub>, C<sub>BD1</sub>

#### C<sub>BOT</sub> and C<sub>SW</sub> are model parameters

|                  | Cutoff                             | Ohmic                              | Saturation                                  |

|------------------|------------------------------------|------------------------------------|---------------------------------------------|

| C <sub>GSO</sub> | CoxWL <sub>D</sub>                 | CoxWL <sub>D</sub>                 | $CoxWL_D$                                   |

| $C_{GDO}$        | $CoxWL_D$                          | $CoxWL_D$                          | $CoxWL_D$                                   |

| C <sub>BG</sub>  |                                    |                                    |                                             |

| C <sub>BS</sub>  | $C_{BS1} = C_{BOT}A_S + C_{SW}P_S$ | $C_{BS1} = C_{BOT}A_S + C_{SW}P_S$ | $C_{BS1} = C_{BOT}A_S + C_{SW}P_S$          |

| C <sub>BD</sub>  | $C_{BD1} = C_{BOT}A_D + C_{SW}P_D$ | $C_{BD1} = C_{BOT}A_D + C_{SW}P_D$ | $C_{BD1} = C_{BOT}A_D + C_{SW}P_D$ 58 of 75 |

## C<sub>BOT</sub> and C<sub>SW</sub> model parameters

| CAPACITANCE PARAMETERS N+ P+ POLY | M1 | M2 | МЗ | M4 | M5 | М6 | R W | D N W M5   | SP N W           | UNITS   |

|-----------------------------------|----|----|----|----|----|----|-----|------------|------------------|---------|

| Area (substrate) 942 1163 106     | 34 | 14 | 9  | 6  | 5  | 3  | _   | _ <u>_</u> | $1\overline{2}5$ | aF/um^2 |

| Area (N+active) 8484              | 55 | 20 | 13 | 11 | 9  | 8  |     |            |                  | aF/um^2 |

| Area (P+active) 8232              |    |    |    |    |    |    |     |            |                  | aF/um^2 |

| Area (poly)                       | 66 | 17 | 10 | 7  | 5  | 4  |     |            |                  | aF/um^2 |

| Area (metal1)                     |    | 37 | 14 | 9  | 6  | 5  |     |            |                  | aF/um^2 |

| Area (metal2)                     |    |    | 35 | 14 | 9  | 6  |     |            |                  | aF/um^2 |

| Area (metal3)                     |    |    |    | 37 | 14 | 9  |     |            |                  | aF/um^2 |

| Area (metal4)                     |    |    |    |    | 36 | 14 |     |            |                  | aF/um^2 |

| Area (metal5)                     |    |    |    |    |    | 34 |     |            | 984              | aF/um^2 |

| Area (r well) 920                 |    |    |    |    |    |    |     |            |                  | aF/um^2 |

| Area (d well)                     |    |    |    |    |    |    | 582 |            |                  | aF/um^2 |

| Area (no well) 137                |    |    |    |    |    |    |     |            |                  | aF/um^2 |

| Fringe (substrate) (212)(235)     | 41 | 35 | 29 | 21 | 14 |    |     |            |                  | aF/um   |

| Fringe (poly)                     | 70 | 39 | 29 | 23 | 20 | 17 |     |            |                  | aF/um   |

| Fringe (metall)                   |    | 52 |    |    |    | 19 |     |            |                  | aF/um   |

| Fringe (metal2)                   |    |    | 48 | 35 | 27 |    |     |            |                  | aF/um   |

| Fringe (metal3)                   |    |    |    | 53 |    | 27 |     |            |                  | aF/um   |

| Fringe (metal4)                   |    |    |    |    | 58 | 35 |     |            |                  | aF/um   |

| Fringe (metal5)                   | _  |    |    |    |    | 55 |     |            |                  | aF/um   |

| Overlap (N+active) 895            |    |    |    |    |    |    |     |            |                  | aF/um   |

| Overlap (P+active) 737            | /  |    |    |    |    |    |     |            |                  | aF/um   |

59

## Types of Capacitors in MOSFETs

- 1. Fixed Capacitors

- a. Fixed Geometry

- b. Junction

- 2. Operating Region Dependent

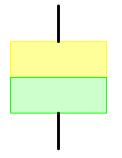

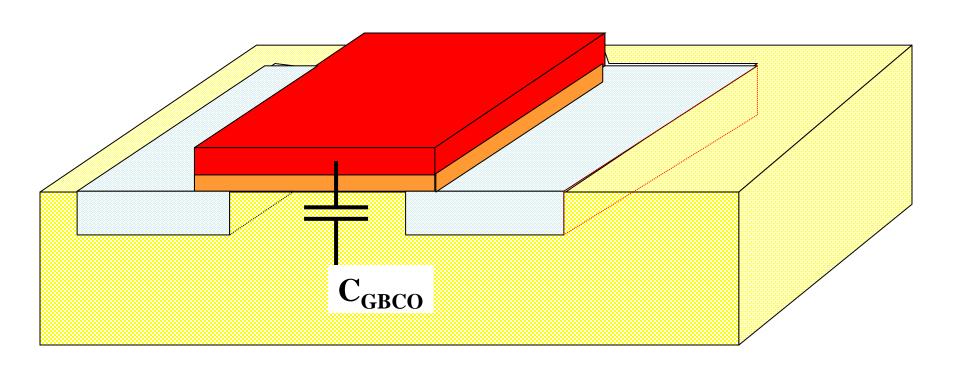

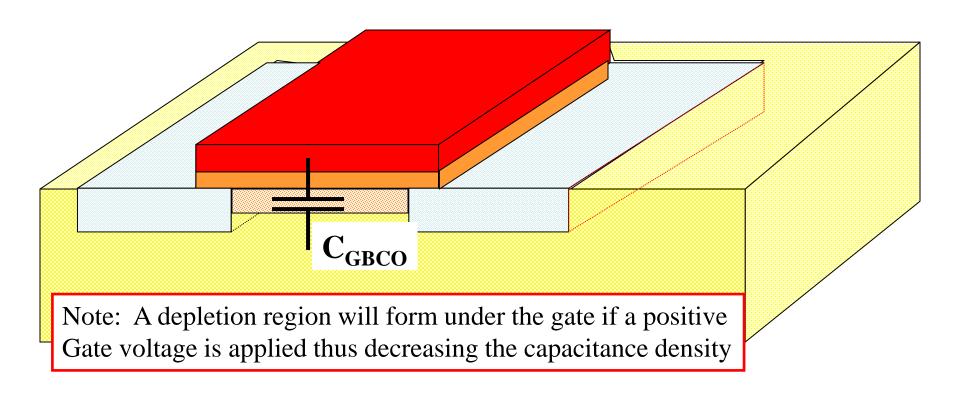

## Parasitic Capacitors in MOSFET Operation Region Dependent -- Cutoff

**Cutoff Capacitor: C**<sub>GBCO</sub>

## Parasitic Capacitors in MOSFET Operation Region Dependent -- Cutoff

**Cutoff Capacitor:** C<sub>GBCO</sub>

#### Operation Region Dependent and Fixed -- Cutoff

Overlap Capacitors: C<sub>GDO</sub>, C<sub>GSO</sub>

Junction Capacitors: C<sub>BS1</sub>, C<sub>BD1</sub>

**Cutoff Capacitor: C**<sub>GBCO</sub>

|                  | Cutoff                                                          | Ohmic | Saturation |

|------------------|-----------------------------------------------------------------|-------|------------|

| C <sub>GSO</sub> | CoxWL <sub>D</sub>                                              |       |            |

| $C_{GDO}$        | CoxWL <sub>D</sub>                                              |       |            |

| C <sub>BG</sub>  | CoxWL (or less)                                                 |       |            |

| C <sub>BS</sub>  | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> |       |            |

| C <sub>BD</sub>  | $C_{BOT}A_D+C_{SW}P_D$                                          |       |            |

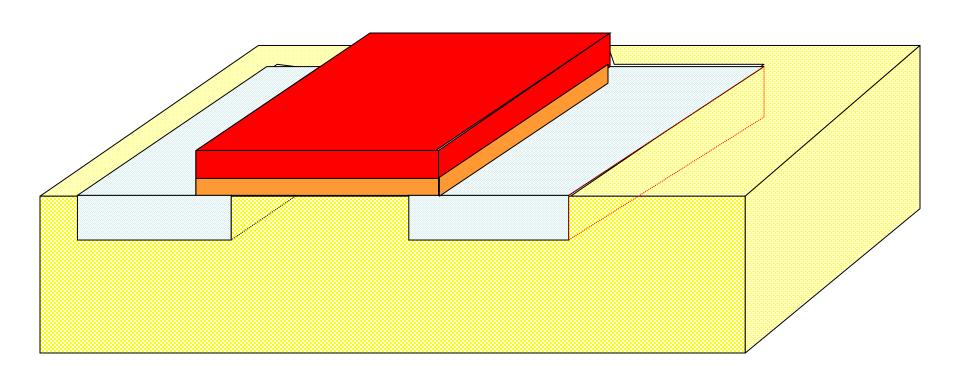

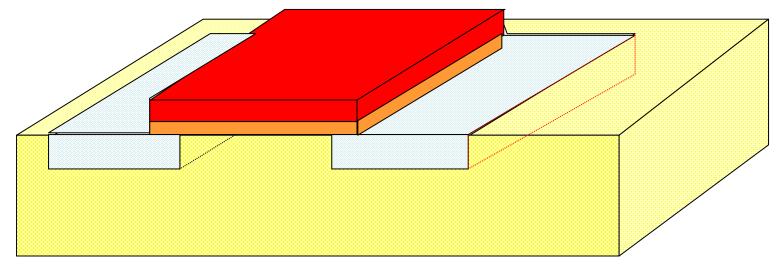

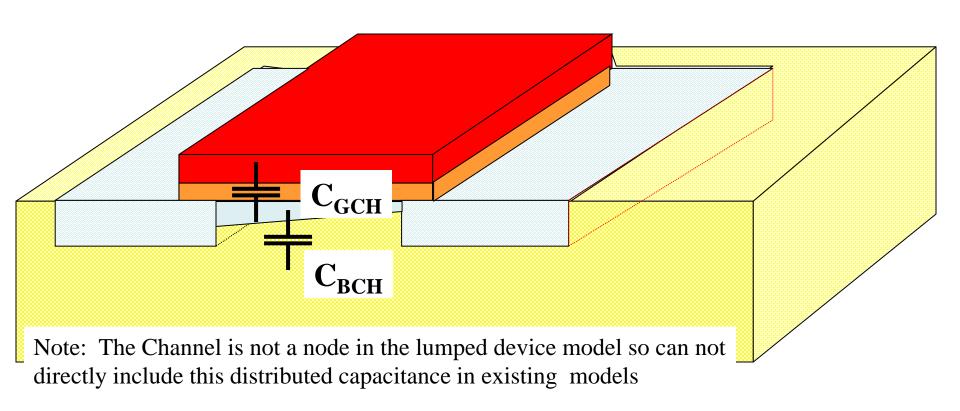

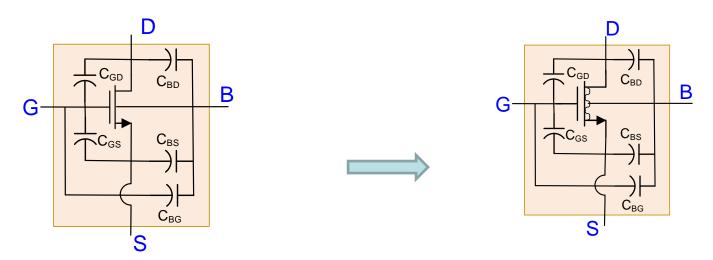

## Parasitic Capacitors in MOSFET Operation Region Dependent -- Ohmic

Note: The distributed channel capacitance is usually lumped and split evenly between the source and drain nodes

Ohmic Capacitor:  $C_{GCH}$ ,  $C_{BCH}$

## Parasitic Capacitors in MOSFET Operation Region Dependent and Fixed -- Ohmic

Overlap Capacitors: C<sub>GDO</sub>, C<sub>GSO</sub>

Junction Capacitors: C<sub>BS1</sub>, C<sub>BD1</sub>

Ohmic Capacitor: C<sub>GCH</sub>, C<sub>BCH</sub>

Lumped C<sub>GC</sub> and C<sub>BC</sub> to analytically avoid dealing with distributed capacitance

|                 | Cutoff                                                          | Ohmic                                                                                    | Saturation |

|-----------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|------------|

| C <sub>GS</sub> | CoxWL <sub>D</sub>                                              | 0.5CoxWL                                                                                 |            |

| C <sub>GD</sub> | CoxWL <sub>D</sub>                                              | 0.5CoxWL                                                                                 |            |

| C <sub>BG</sub> | CoxWL (or less)                                                 | 0                                                                                        |            |

| C <sub>BS</sub> | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> +0.5WLC <sub>BOTCH</sub> |            |

| C <sub>BD</sub> | $C_{BOT}A_D + C_{SW}P_D$                                        | C <sub>BOT</sub> A <sub>D</sub> +C <sub>SW</sub> P <sub>D</sub> +0.5WLC <sub>BOTCH</sub> |            |

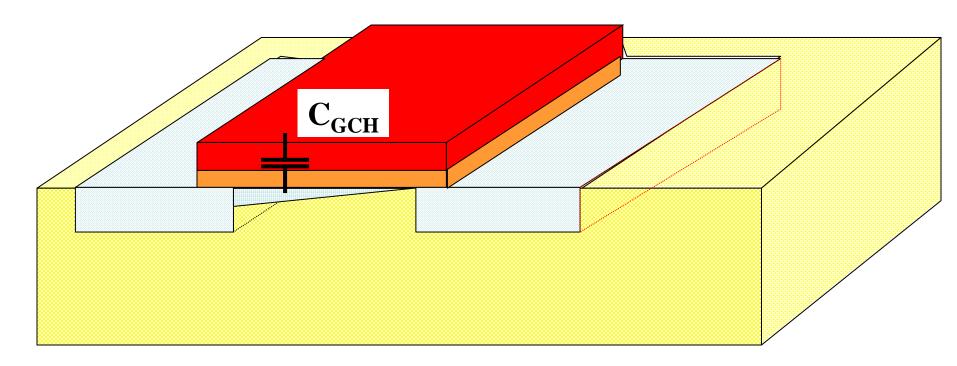

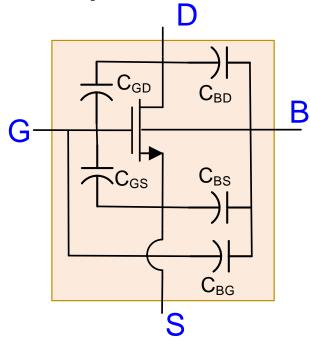

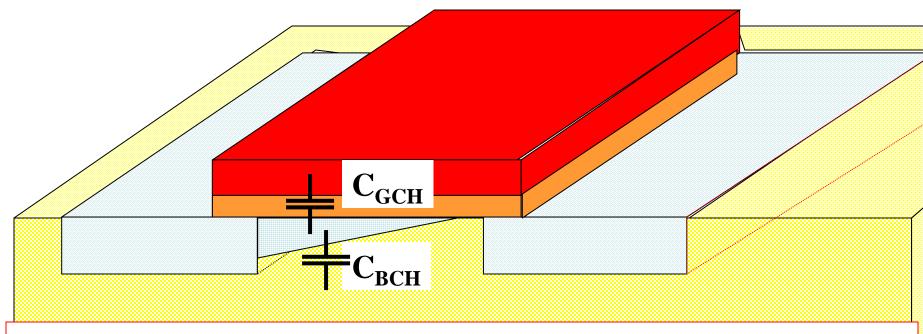

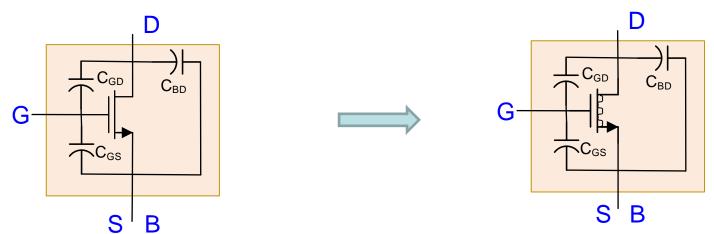

#### Operation Region Dependent -- Saturation

Note: Since the channel is an extension of the source when in saturation, the distributed capacitors to the channel are generally lumped to the source node

**Saturation Capacitors:** C<sub>GCH</sub>, C<sub>BCH</sub>

#### Operation Region Dependent and Fixed -- Saturation

Overlap Capacitors: C<sub>GDO</sub>, C<sub>GSO</sub>

Junction Capacitors: C<sub>BS1</sub>, C<sub>BD1</sub>

Saturation Capacitors:  $C_{GCH}$ ,  $C_{BCH}$

- 2/3 C<sub>OX</sub>WL is often attributed to C<sub>GCH</sub> to account for LD and saturation

- This approximation is reasonable for minimum-length devices but not so good for longer devices

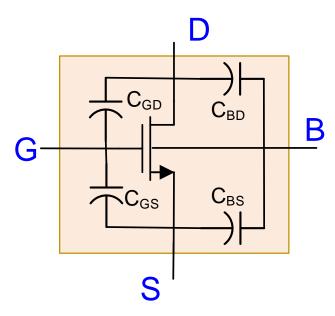

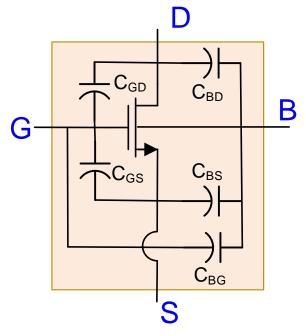

G C<sub>BD</sub> C<sub>BD</sub> B

C<sub>BS</sub> C<sub>BS</sub>

Lumped C<sub>GC</sub> and C<sub>BC</sub> to analytically avoid dealing with distributed capacitance

|                 | Cutoff                   | Ohmic                                                                                    | Saturation                                                                                 |

|-----------------|--------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| C <sub>GS</sub> | CoxWL <sub>D</sub>       | 0.5C <sub>OX</sub> WL                                                                    | CoxWL <sub>D</sub> +(2/3)C <sub>OX</sub> WL                                                |

| $C_{GD}$        | CoxWL <sub>D</sub>       | 0.5C <sub>OX</sub> WL                                                                    | CoxWL <sub>D</sub>                                                                         |

| C <sub>BG</sub> | CoxWL (or less)          | 0                                                                                        | 0                                                                                          |

| C <sub>BS</sub> | $C_{BOT}A_S+C_{SW}P_S$   | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> +0.5WLC <sub>BOTCH</sub> | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> +(2/3)WLC <sub>BOTCH</sub> |

| C <sub>BD</sub> | $C_{BOT}A_D + C_{SW}P_D$ | C <sub>BOT</sub> A <sub>D</sub> +C <sub>SW</sub> P <sub>D</sub> +0.5WLC <sub>BOTCH</sub> | $C_{BOT}A_D + C_{SW}P_D$                                                                   |

|                 | Cutoff                   | Ohmic                                                                                    | Saturation                                  |

|-----------------|--------------------------|------------------------------------------------------------------------------------------|---------------------------------------------|

| C <sub>GS</sub> | CoxWL <sub>D</sub>       | 0.5C <sub>OX</sub> WL                                                                    | CoxWL <sub>D</sub> +(2/3)C <sub>OX</sub> WL |

| C <sub>GD</sub> | CoxWL <sub>D</sub>       | 0.5C <sub>OX</sub> WL                                                                    | CoxWL <sub>D</sub>                          |

| C <sub>BG</sub> | CoxWL (or less)          | 0                                                                                        | 0                                           |

| C <sub>BS</sub> | $C_{BOT}A_S + C_{SW}P_S$ | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> +0.5WLC <sub>BOTCH</sub> | $C_{BOT}A_S+C_{SW}P_S+(2/3)WLC_{BOTCH}$     |

| C <sub>BD</sub> | $C_{BOT}A_D + C_{SW}P_D$ | C <sub>BOT</sub> A <sub>D</sub> +C <sub>SW</sub> P <sub>D</sub> +0.5WLC <sub>BOTCH</sub> | $C_{BOT}A_D + C_{SW}P_D$                    |

71 of 75

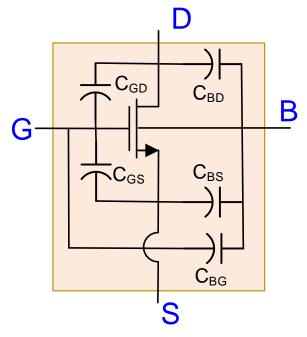

High Frequency Large Signal Model

High Frequency Small Signal Model

Often  $V_{BS}=0$  and  $C_{BG}=0$ , so simplifies to

### Parasitic Capacitance Implications

The parasitic capacitances inherently introduce an upper limit on how fast either digital circuits or analog circuits can operate in a given process

Two parameters,  $f_{MAX}$  and  $f_{T}$ , (not defined yet) are two metric that are used to specify the fundamental speed limit in a semiconductor process

The dominant parasitic capacitances for most circuits are  $C_{GS}$  and  $C_{BD}$

## Stay Safe and Stay Healthy!

### End of Lecture 35